# An Intra-Body Power Transfer System with Dual Maximum Resonant Power **Tracking Loop Achieving Improved Power Efficiency**

Hyungjoo Cho<sup>1</sup>, Hoyong Sung<sup>1</sup>, Gichan Yun<sup>1</sup>, Ji-Hoon Suh<sup>1</sup>, Sohmyung Ha<sup>2</sup>, and Minkyu Je<sup>1</sup> <sup>1</sup>School of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST) <sup>2</sup>School of Electrical Engineering, New York University Abu Dhabi E-mail: hyungjoo.cho@kaist.ac.kr

### Introduction & Issues in Prior Work

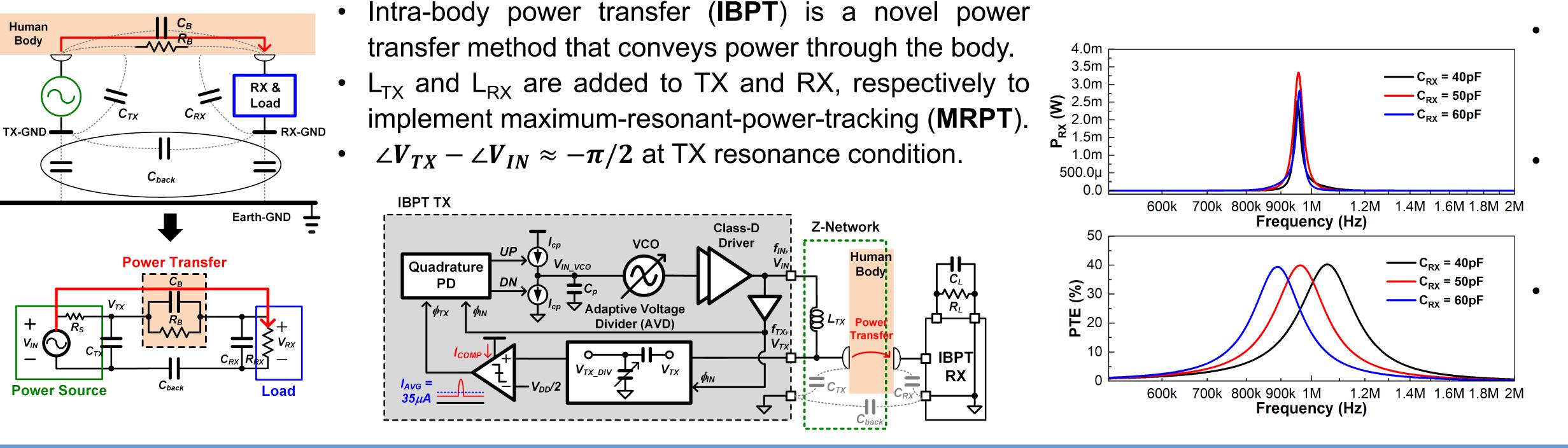

- Previous IBPT TX consumes lots of power at the comparator to minimize delay.

- Maximum power transfer frequency ≠ maximum power transfer efficiency frequency

- MRPT is required for both TX and RX. TX MRPT maximizes  $V_{TX}$ , and the RX MRPT maximizes PTE.

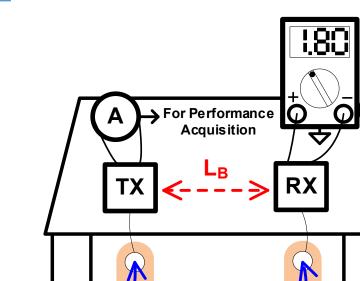

## **Overall System**

IBPT TX

# **Measurement Results**

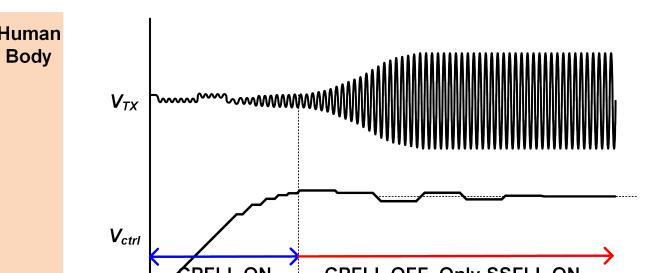

#### **Measurement Setup & Chip Micrograph**

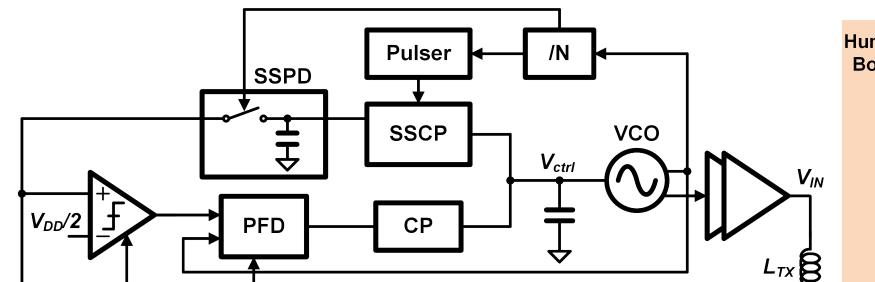

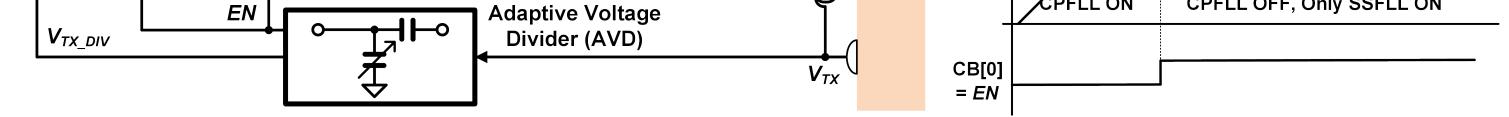

- TX employs a FLL-based MRPT loop that locks at the frequency, where  $\phi_{\Lambda}$ is  $\pi/2$ .  $(\phi_{\Delta} = \angle V_{IN} - \angle V_{TX} = \phi_{IN} - \phi_{TX})$

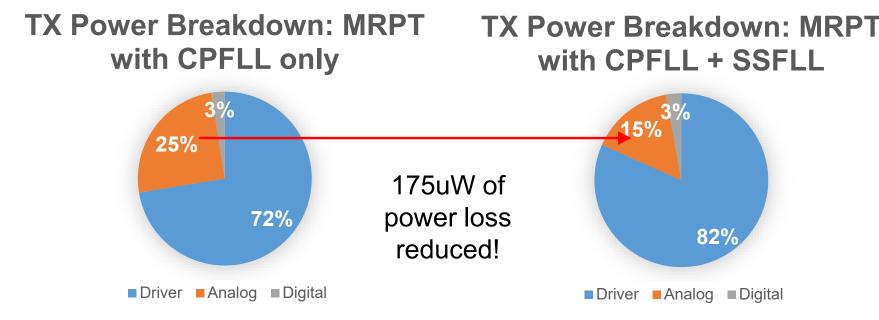

- Charge pump (CP) FLL + sub-sampling (SS) FLL.

- Power consuming CPFLL helps fast and stable start-up.

- C-bank control bit at adaptive voltage divider (AVD) is used as enable (EN) for CPFLL.

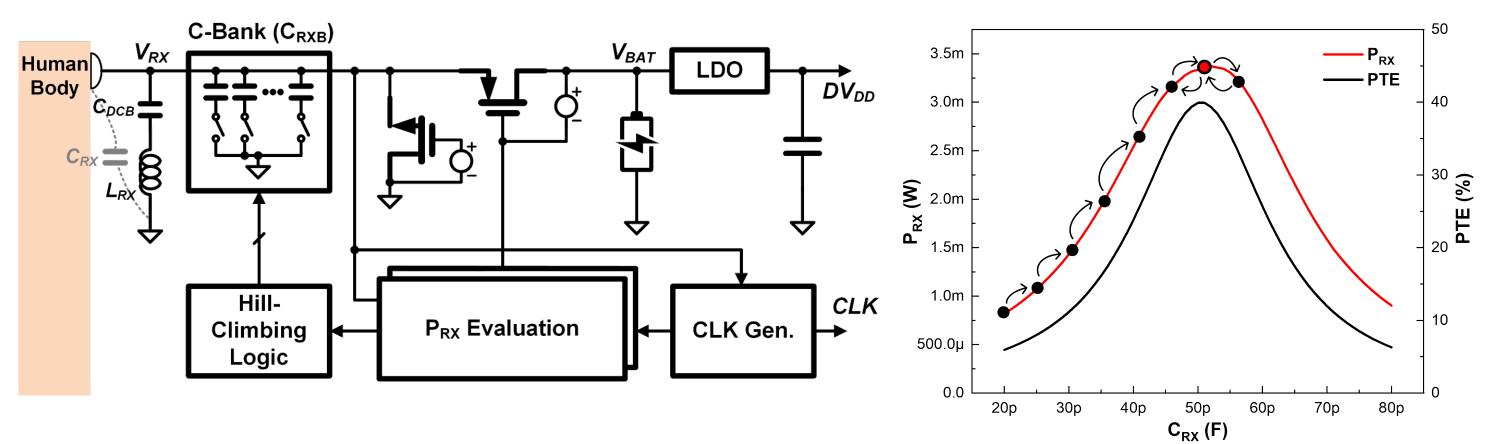

#### **IBPT RX**

- Battery load target.

- $L_{RX}$  resonates with  $C_{RX} || C_{RXB}$

- Hill-climbing algorithm controlling  $C_{RXB}$  can find maximum  $P_{RX}$  & PTE condition.

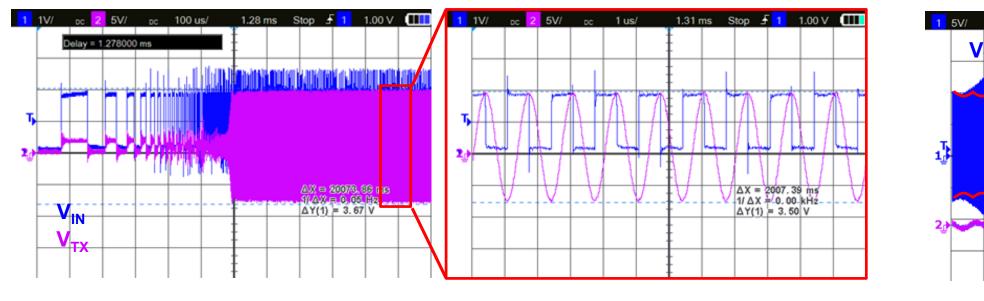

To verify TRX operation, body channel model is implemented on the breadboard and measured.

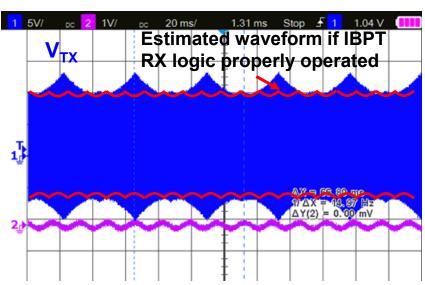

#### **Measurement Results**

- TX operates well  $\rightarrow$  TX power efficiency improves

- RX does not operates well  $\rightarrow$  Logic cannot find the optimum C<sub>RX</sub>, but oscillates.

- Potential issues in  $P_{RX}$  Evaluation block at IBPT RX: leakage current makes an error while comparing  $V_{NOW}$  and  $V_{PAST}$ .

### **Summary & Conclusion**

- Power loss at TX significantly reduced due to using temporarily-on CPFLL and always-on SSFLL.

- Hill-climbing algorithm controlling  $C_{RXR}$  was implemented, but did not operated well because of leakage current.

- Proposed IBPT system can make both maximum power and efficiency by implementing dual MRPT both at TX and RX.

## Acknowledgement

• The chip fabrication and EDA tool were supported by the IC Design Education Center (IDEC), Korea.